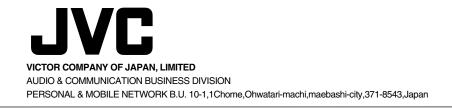

# JVC SERVICE MANUAL

## DVD DIGITAL CINEMA SYSTEM

## TH-A9

TH-A9

## -Safety Precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (A) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

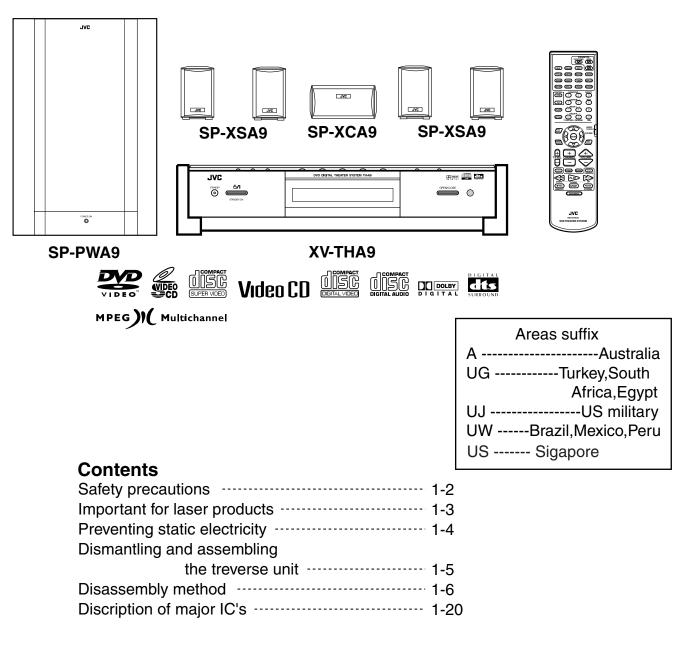

- 5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

#### Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500  $\Omega$  10W resistor paralleled by a 0.15 $\mu$ F AC-type capacitor

between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to eachexposed metal part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. Voltage measured any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

## Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the parts that are printed over with black such as the resistor (-), diode (+) and ICP (-) or identified by the " $\underline{\wedge}$ " mark nearby are critical for safety.

When replacing them, be sure to use the parts of the same type and rating as specified by the manufacturer. (Except the J and C version)

## **Important for Laser Products**

#### 1.CLASS II a LASER PRODUCT

- **2.DANGER :** Invisible laser radiation when open and inter lock failed or defeated. Avoid direct exposure to beam.

- **3.CAUTION :** There are no serviceable parts inside the Laser Unit. Do not disassemble the Laser Unit. Replace the complete Laser Unit if it malfunctions.

- **4.CAUTION :** The compact disc player uses invisible laserradiation and is equipped with safety switches whichprevent emission of radiation when the drawer is open and the safety interlocks have failed or are de feated. It is dangerous to defeat the safety switches.

- **5.CAUTION :** If safety switches malfunction, the laser is able to function.

- **6.CAUTION :** Use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

- ▲ CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

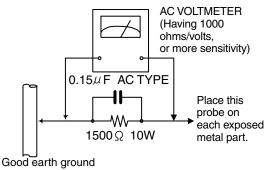

## **Preventing static electricity**

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

## 1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players. Be careful to use proper grounding in the area where repairs are being performed.

## 1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

## 1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

## 1.1.3. Handling the optical pickup

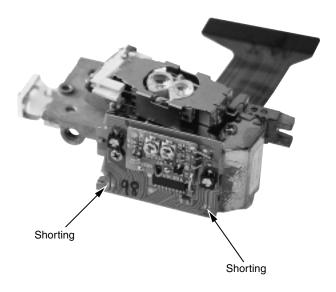

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

## 1.2. Handling the traverse unit (optical pickup)

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

## Dismantling and assembling the traverse unit

## 1. Notice regarding replacement of optical pickup

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs to the optical pickup or connected devices.

(Refer to the section regarding anti-static measures.)

- 1. Do not touch the area around the laser diode and actuator.

- 2. Do not check the laser diode using a tester, as the diode may easily be destroyed.

- 3. It is recommended that you use a grounded soldering iron when shorting or removing the laser diode. Recommended soldering iron: HAKKO ESD-compatible product

- 4. Solder the land on the optical pickup's flexible cable.

- Note : Short the land after shorting the terminal on the flexible cable using a clip, etc., when using an ungrounded soldering iron.

- Note : After shorting the laser diode according to the procedure above, remove the solder according to the text explanation.

## **Disassembly method**

## <Main unit>

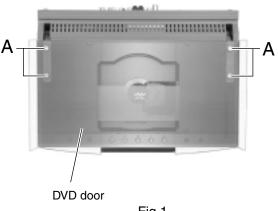

## Removing the DVD door (See Fig.1)

1. Remove the four screws A that retain the DVD door from the top of the unit.

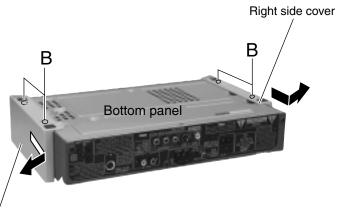

## Removing the right and left side covers (See Fig.2)

- Prior to performing the following procedure, remove the DVD door.

- 1. Remove the four screws (B) that attach the left and right side covers of the unit, from the bottom panel.

- 2. Remove the left and right side covers by moving each of them in the direction of the corresponding arrow.

Fig.2

Left side cover

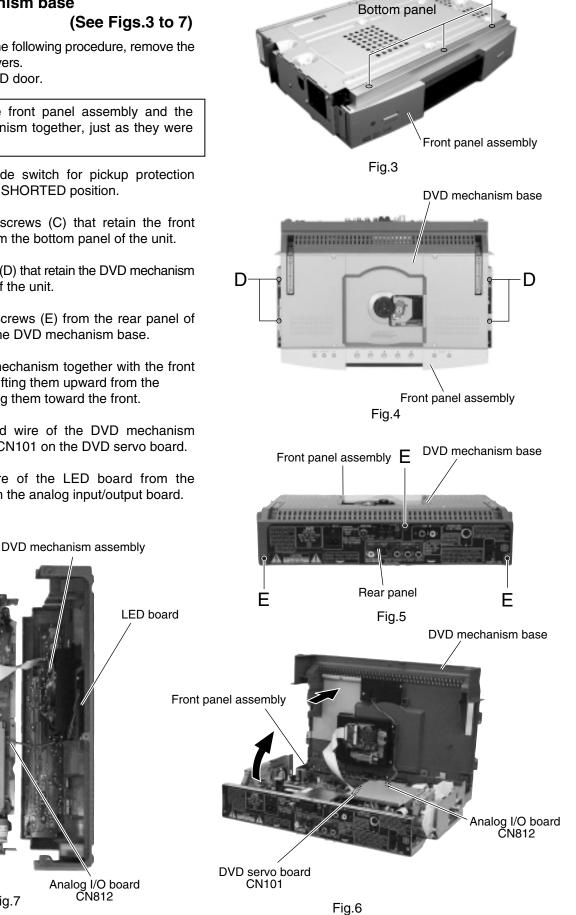

## Removing the front panel assembly and the DVD mechanism base

- · Prior to performing the following procedure, remove the left and right side covers.

- · Also remove the DVD door.

(Note) Remove the front panel assembly and the DVD mechanism together, just as they were assembled.

- · The mechanism slide switch for pickup protection should be set to the SHORTED position.

- 1. Remove the three screws (C) that retain the front panel assembly, from the bottom panel of the unit.

- 2. Remove four screws (D) that retain the DVD mechanism base, from the top of the unit.

- 3. Remove the three screws (E) from the rear panel of the unit that retain the DVD mechanism base.

- 4. Remove the DVD mechanism together with the front panel assembly by lifting them upward from the main unit and moving them toward the front.

- 5. Disconnect the card wire of the DVD mechanism from the connector CN101 on the DVD servo board.

Disconnect the wire of the LED board from the connector CN812 on the analog input/output board.

Fig.7

DVD servo board CN101

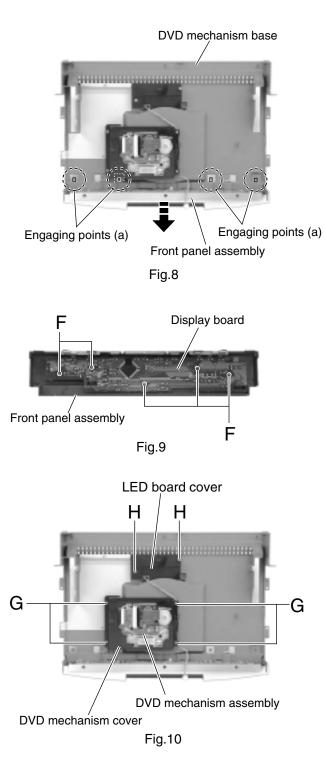

## ■Separating the front panel assembly and the DVD mechanism base (See Fig.8)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

- 1. Remove the front panel assembly and the DVD mechanism base together from the main unit. (See Figs. 3 to 7.)

- 2. On the back of the DVD mechanism base, disengage the four claws at the engaging points (a) that attach the front panel assembly to the DVD mechanism base, and then pull out the front panel assembly in the direction of the arrow to separate it from the DVD mechanism base.

(Note) It is at this stage that the front panel assembly and the DVD mechanism base are separated from each other.

## ■Removing the display board (See Fig.9)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

- Also separate the front panel assembly from the DVD mechanism base.

- 1. Remove the five screws (F) that retain the display board.

## Removing the DVD mechanism assembly (See Figs.10 and 11)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

(Note) This work is possible even when the front panel assembly is attached to the DVD mechanism base.

- 1. Remove the four screws (G) from the back of the DVD mechanism base that retain the DVD mechanism cover.

- 2. Remove the DVD mechanism assembly from the DVD mechanism base.

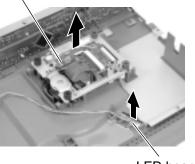

## Removing the LED board (See Figs.10 and 11)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

(Note) This work is possible even when the front panel assembly is attached to the DVD mechanism base.

- 1. Remove two screws (H) that retain the LED board cover, from the back of the DVD mechanism base.

- 2. Remove the LED board by pulling it away from the DVD mechanism base.

DVD mechanism assembly

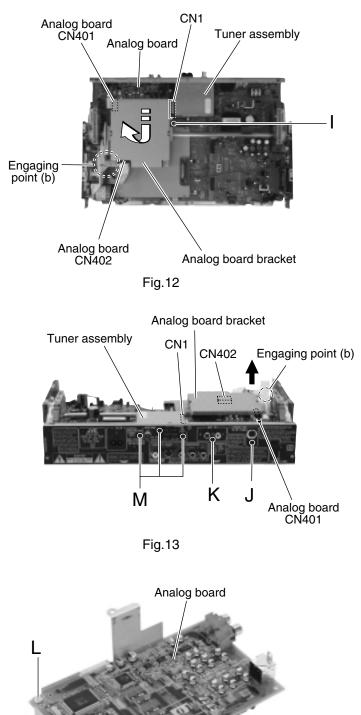

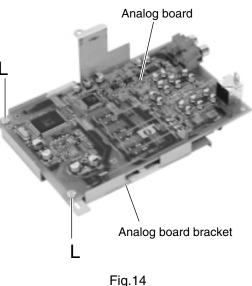

## Removing the analog board (See Figs.12 to 14)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

- Also remove the front panel assembly and DVD mechanism base.

- 1. Disconnect the card wires from the connectors CN401 and CN402 on the analog board.

- 2. Remove the screw (I) that retains the analog board bracket from the top of the unit.

- 3. Remove the screw (J) and the screw (K) that retain the analog board from the rear panel of the unit.

- 4. Disengage the analog board bracket and the gear motor assembly by moving the engaged part (b) upward. Then move the analog board in the direction of the arrow, and remove it as if pulling it out of the rear panel.

- 5. Remove two screws (L) that attach the analog board to the analog board bracket.

## Removing the tuner assembly (See Figs.12 and 13)

- Prior to performing the following procedure, remove the left and right side covers.

- · Also remove the DVD door.

- Also remove the front panel assembly and the DVD mechanism base.

- 1. Remove the three screws (M) that retain the tuner assembly, from the rear panel of the unit.

- 2. Disconnect the card wire from the connector CN1 on the tuner assembly.

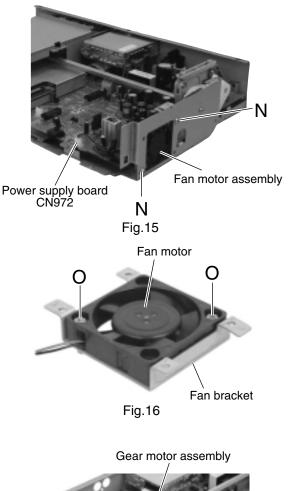

## Removing the fan motor assembly (See Figs.15 and 16)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

- Also remove the front panel assembly and the DVD mechanism base.

- 1. Disconnect the wire from the connector CN972 on the power supply board.

- 2. Remove the two screws (N) that retain the fan motor assembly, from the right side of the unit.

- 3. Remove the two screws (O) that attach the fan motor assembly to the fan bracket.

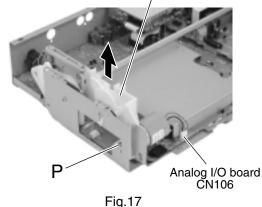

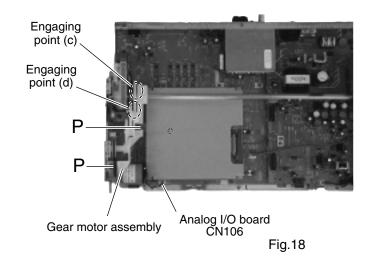

## Removing the gear motor assembly (See Figs.17 to 19)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

- Also remove the front panel assembly and the DVD mechanism base.

- $\cdot\,$  Also remove the analog board.

- 1. Disconnect the wire from the connector CN106 on the analog input/output board.

- 2. Remove the two screws (P) that retain the gear motor assembly and remove the assembly in the direction of the arrow.

(Note) When reassembling, check that the gear motor assembly is engaged properly with the door arm assembly at the engaging points (c) and (d).

Gear motor

Q

- 3. Remove the belt from the gear motor assembly.

- 4. Remove two screws Q that retain the gear motor.

Belt

Fig.19

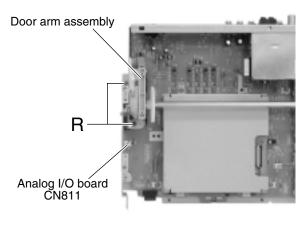

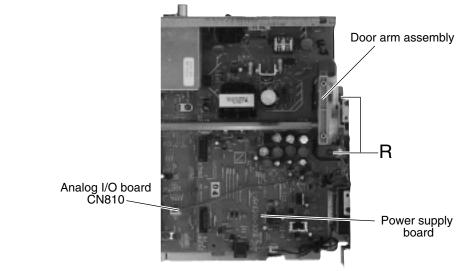

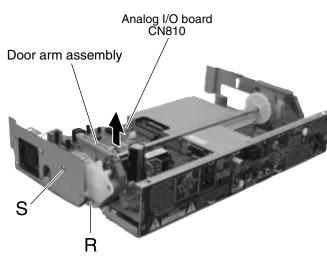

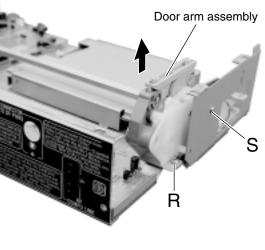

## Removing the door arm assembly (See Figs.20 to 23)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

- Also remove the front panel assembly and the DVD mechanism base.

- Also remove the analog board.

- $\cdot\,$  Also remove the gear motor assembly.

- 1. Disconnect the wires from the connectors CN810 and CN811 on the analog input/output board.

- 2. Remove the four screws (R) that retain the door arm assembly, from the top of the unit.

- 3. Remove the two screws (S) that retain the door arm assembly, from the left and right sides of the unit.

Fig.23

Fig.22

TH-A9

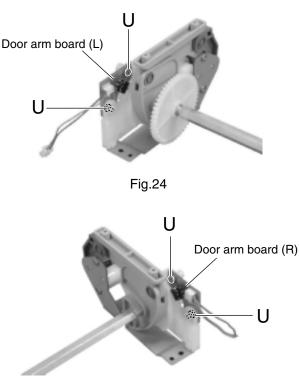

## Removing the door arm boards (L) and (R) (See Figs.24 and 25)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

- Also remove the front panel assembly and the DVD mechanism base.

- Also remove the analog board.

- $\boldsymbol{\cdot}$  Also remove the gear motor assembly.

- $\cdot$  Also remove the door arm assembly.

- 1. Remove the two screws (U) that retain the door arm board (L).

- 2. Remove two screws (U) that retain the door arm board (R).

Fig.27

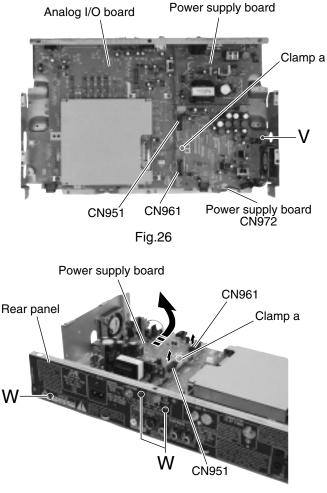

## Removing the power supply board (See Figs.26 and 27)

- Prior to performing the following procedure, remove the left and right side covers.

- Also remove the DVD door.

- Also remove the front panel assembly and the DVD mechanism base.

- · Also remove the analog board.

- Also remove the gear motor assembly. Also remove the door arm assembly.

- 1. Remove the screw (V) that retains the power supply board, from the top of the unit.

- 2. Remove three screws (W) that retain the power supply board, from the rear panel of the unit.

- 3. Pull out the power supply board from clamp a.

- 4. Disconnect the wire from the connector CN972 on the power supply board, and then remove the power supply board in the direction of the arrow while unplugging the connectors CN951 and CN961 from the analog input/output board.

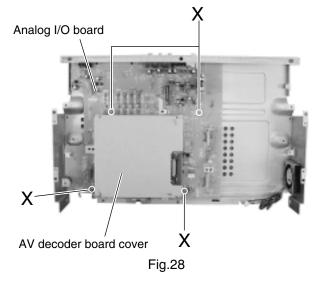

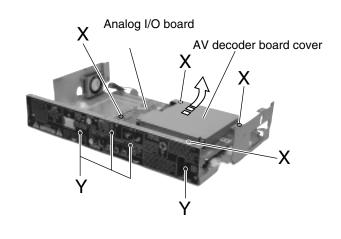

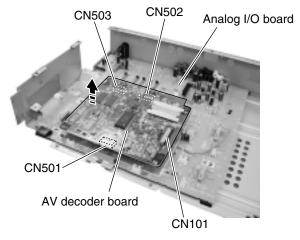

## Removing the AV decoder board and analog input/output board

(See Figs.28 to 30)

- Prior to performing the following procedure, remove the left and right side covers.

- · Also remove the DVD door.

- Also remove the front panel assembly and DVD mechanism base.

- Also remove the analog board.

- · Also remove the gear motor assembly.

- · Also remove the door arm assembly.

- 1. Remove the three screws (X) that retain the AV decoder board cover, from the top of the unit and remove the screw (X) that retains the analog input/output board.

- 2. IF it is required to separate the AV decoder board from the analog input/output board, unplug the connectors CN501, CN502 and CN503 on the AV decoder board from the analog input/output board.

(Note) The analog input/output board can be removed even when it is engaged with the AV decoder board.

3. Remove the four screws (Y) that retain the analog input/output board, from the rear panel of the unit. This procedure also detaches the rear panel.

Fig.30

## **Disassembly method**

<Speaker>

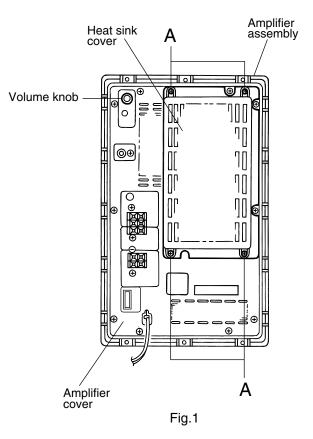

## ■Removing the heat sink cover (See Fig.1)

1. Remove the four screws A attaching the heat sink cover.

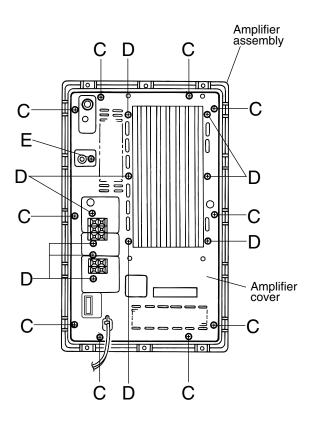

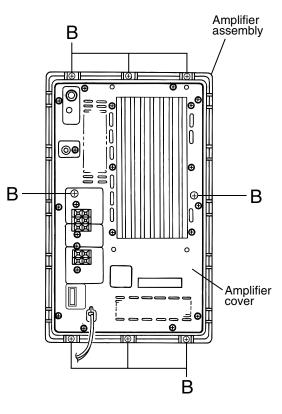

## ■Removing the amplifier assembly and the amplifier cover (See Figs.2 and 3)

- Prior to performing the following procedure, remove the heat sink.

- 1. Remove the eigth screws B attaching the amplifier assembly on the back of the body.

- 2. Move the amplifier assembly backward and disconnect the harness from connector CN109 in the lower part of the amplifier assembly.

- 3. Pull out the volume knob.

- 4. Remove the ten screws C attaching the amplifier cover.

- 5. Remove the ten screws D and the one screw E attaching the amplifier cover.

Fig.2

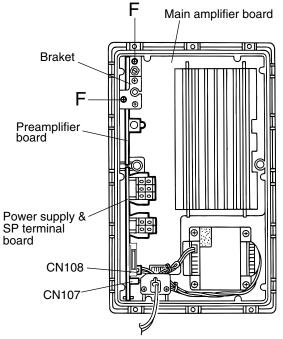

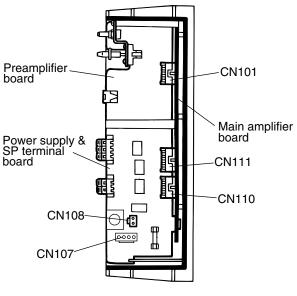

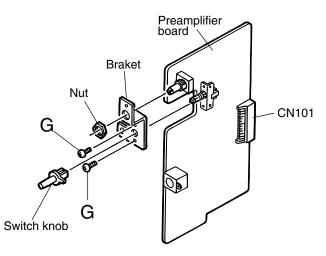

## Removing the preamplifier board (See Figs.4 to 6)

- Prior to performing the following procedure, remove the heat sink cover, the amplifier assembly and the amplifier cover.

- 1. Remove the two screws F attaching the preamplifier board to the bracket.

- 2. Disconnect connector CN101 on the preamplifier board from the main amplifier board.

- 3. Pull out the switch knob.

- 4. Remove the nut and the two screws G attaching the bracket.

## Removing the power supply & SP terminal board (See Figs.4 and 5)

- Prior to performing the following procedure, remove the heat sink cover, amplifier assembly and the amplifier cover.

- 1. Disconnect the wire from the connectors CN107 and CN108 on the power supply & SP terminal board.

- 2. Unplug the connectors CN110 and CN111 on the power supply & SP terminal board from the main amplifier board.

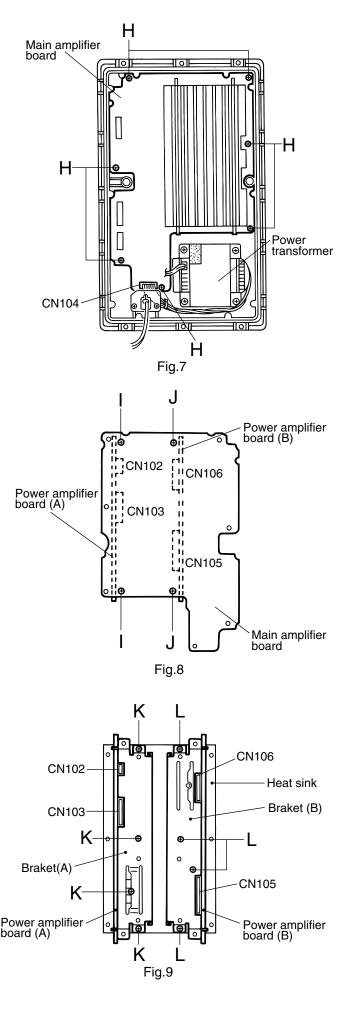

## Removing the Main amplifier Board (See Figs.7 and 8)

- Prior to performing the following procedure, remove the heat sink cover, the amplifier board, the amplifier cover, the preamplifier board and the power supply & SP terminal board.

- 1. Disconnect the harness from connector CN104 on the main amplifier board.

- 2. Remove the seven screws H and the main amplifier board with the heat sink.

- 3. Remove the two screws I attaching the power amplifier board (A) and the two screws J attaching the power amplifier board (B) on the underside of the main amplifier board.

- 4. Disconnect connector CN102 and CN103 on the power amplifier board (A) and CN105 and CN106 on the power amplifier board (B) from the main amplifier board respectively.

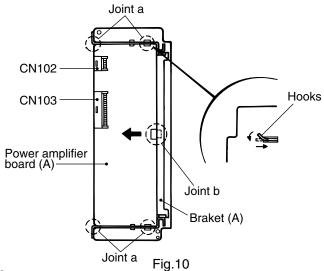

## Removing the power amplifier board (A) (See Figs.9 and 10)

- Prior to performing the following procedure, remove the heat sink cover, amplifier assembly, the amplifier cover, the preamplifier board, the power supply & SP terminal board, the main amplifier board.

- 1. Remove the four screws K attaching the power amplifier board (A) to the heat sink.

- 2. Release the four joint hooks a bent and attached to the outside of the power amplifier board (A).

- 3. Move the power amplifier board (A) in the direction of the arrow to release joint b and remove the power amplifier board (A) from the bracket (A).

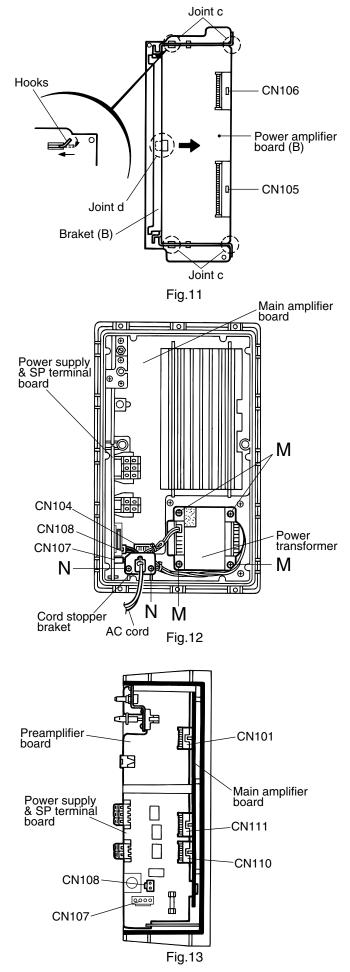

## Removing the power amplifier board (B) (See Figs.9 and 11)

- Prior to performing the following procedure, remove the heat sink cover, the amplifier assembly, the amplifier cover, the preamplifier board, the power supply & SP terminal board, the main amplifier board and power amplifier board (A).

- 1. Remove the four screws L attaching the power amplifier board (B) to the heat sink.

- 2. Release the four joint hooks c bent and attached to the outside of the power amplifier board (B).

- 3. Move the power amplifier board (B) in the direction of the arrow to release joint d and remove the power amplifier board (B) from the bracket (B).

## Removing the power transformer (See Figs.12 and 13)

- Prior to performing the following procedure, remove the heat sink cover, the amplifier assembly, the amplifier cover, the preamplifier board, the power supply & SP terminal board, the main amplifier board, the power amplifier board (A) and power amplifier board (B).

- 1. Disconnect the harness from connector CN104 on the main amplifier board.

- 2. Disconnect the wire from connector CN107 on the power supply & SP terminal board.

- 3. Remove the four screws M attaching the power transformer.

## Removing the AC power cord

(See Fig.12)

- Prior to performing the following procedure, remove the heat sink cover, the amplifier assembly, the amplifier cover, the preamplifier board, the power supply & SP terminal board, the main amplidier board, the power amplifier board (A), the power amplifier board (B) and power transformer.

- 1. Disconnect the wire from connector CN108 on the power supply & SP terminal board.

- 2. Remove the two screws N attaching the AC power cord.

## ■Initialization of EEPROM

- 1. Make sure that no disc is present on the tray.

- 2. At first push the power switch to be on. Then the door slides to the position to be able to push the stop button. After that pull AC plug out.

- 3. While holding the STOP and OPEN/CLOSE keys on the main unit depressed, turn on the primary power supply.

- 4. The FL display should show "TEST  $* * \pm$ ".

|    | * * | ¥ |

|----|-----|---|

| А  | Α   | 4 |

| UG | 2U  | 2 |

| UJ | JC  | 1 |

| UW | 4U  | 4 |

- 5. Press the ENTER key on the remote controller. Initialization of the EEPROM starts (and lasts for about 3 seconds). The initialization has completed when the FL display shows "EEPROM" at the center.

- 6. Now the EEPROM initialization is complete.No key is accepted during the EEPROM initialization.To exit from the test mode, press the POWER key to enter the STAND-BY mode.

## Display of the laser current value

- 1. While holding the STOP and OPEN/CLOSE keys on the main unit depressed, plug the AC power cord into the power outlet.

- 2. The FL display should show "TEST".

Note: When the power is in the STAND-BY mode or OFF, the stop key is hidden behind the door. Therefore, to facilitate the entry in the test mode, slide the door in advance so that the STOP key can be pressed even when the AC power is turned off by unplugging the AC power cord.

- 3. Press the "5" key on the remote controller in the test mode. The DVD laser will turn on and the FL display will show a message such as "03EXXXX". As the FL display shows a hexadecimal value, check the actual current value by referring to the conversion table to see if it is OK or not. (The actual laser current value is calculated by subtracting 15 mA from the value obtained with the conversion table.)

- 4. To exit from the test mode, press the POWER key to enter the STAND-BY (power off) mode.

## FL Display conversion table

## 1.Current

|           | Current(mA) |    |            | Current(mA) |    |           | Current(mA) |    |

|-----------|-------------|----|------------|-------------|----|-----------|-------------|----|

| 001c,001b | 25          | OK | 03E5       | 59          | OK | 03AF,03AE | 93          | NG |

| 001A      | 26          | OK | 03E4,03E3  | 60          | OK | 03Ad      | 94          | NG |

| 0019,0018 | 27          | OK | 03E2       | 61          | OK | 03Ac,03Ab | 95          | NG |

| 0017      | 28          | ОК | 03E1,03E0  | 62          | ОК | 03AA,03A9 | 96          | NG |

| 0016,0015 | 29          | ОК | 03dF,03dE, | 63          | ОК | 03A8      | 97          | NG |

| 0014,0013 | 30          | ОК | 03dd       | 64          | ОК | 03A7,03A6 | 98          | NG |

| 0012      | 31          | ОК | 03dc,03db  | 65          | NG | 03A5      | 99          | NG |

| 0011,0010 | 32          | ОК | 03dA       | 66          | NG | 03A4,03A3 | 100         | NG |

| 000f      | 33          | ОК | 03d9,03d8  | 67          | NG | 03A2,03A1 | 101         | NG |

| 000e,000d | 34          | ОК | 03d7,03d6  | 68          | NG | 03A0      | 102         | NG |

| 000c,000b | 35          | ОК | 03d5       | 69          | NG | 039F,039E | 103         | NG |

| 000A      | 36          | ОК | 03d4,03d3  | 70          | NG | 039d,039c | 104         | NG |

| 0009,0008 | 37          | ОК | 03d2       | 71          | NG | 039b      | 105         | NG |

| 0007      | 38          | ОК | 03d1,03d0  | 72          | NG | 039A,0399 | 106         | NG |

| 0006,0005 | 39          | ОК | 03cF,03cE  | 73          | NG | 0398      | 107         | NG |

| 0004,0003 | 40          | ОК | 03cd       | 74          | NG | 0397      | 108         | NG |

| 0002      | 41          | ОК | 03cc,03cb  | 75          | NG |           |             |    |

| 0001,0000 | 42          | ОК | 03cA,03c9  | 76          | NG |           |             |    |

| 03FF      | 43          | ОК | 03c8       | 77          | NG |           |             |    |

| 03FE,03Fd | 44          | ОК | 03c7,03c6  | 78          | NG |           |             |    |

| 03Fc,03Fb | 45          | ОК | 03c5       | 79          | NG |           |             |    |

| 03FA      | 46          | ОК | 03c4,03c3  | 80          | NG |           |             |    |

| 03F9,03F8 | 47          | ОК | 03c2,03c1  | 81          | NG |           |             |    |

| 03F7      | 48          | ОК | 03c0       | 82          | NG |           |             |    |

| 03F6,03F5 | 49          | ОК | 03bF,03bE  | 83          | NG |           |             |    |

| 03F4,03F3 | 50          | ОК | 03bd       | 84          | NG |           |             |    |

| 03F2      | 51          | ОК | 03bc,03bb  | 85          | NG |           |             |    |

| 03F1,03F0 | 52          | ОК | 03bA,03b9  | 86          | NG |           |             |    |

| 03EF,03EE | 53          | ОК | 03b8       | 87          | NG |           |             |    |

| 03Ed      | 54          | ОК | 03b7,03b6  | 88          | NG |           |             |    |

| 03Ec,03Eb | 55          | ОК | 03b5       | 89          | NG |           |             |    |

| 03EA      | 56          | ОК | 03b4,03b3  | 90          | NG |           |             |    |

| 03E9,03E8 | 57          | ОК | 03b2,03b1  | 91          | NG |           |             |    |

| 03E7,03E6 | 58          | ОК | 03b0       | 92          | NG |           |             |    |

## TH-A9 Discription of major IC's

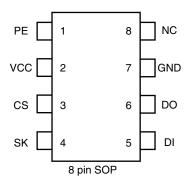

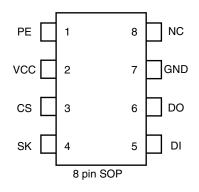

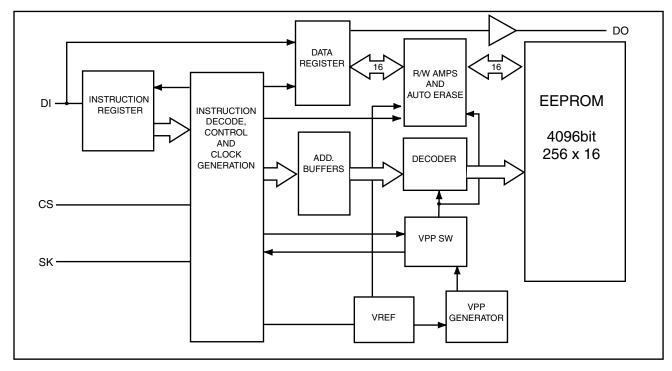

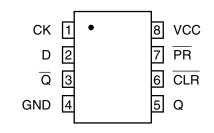

## ■ AK93C65AF-X(IC403) : EEPROM

1.Terminal layout

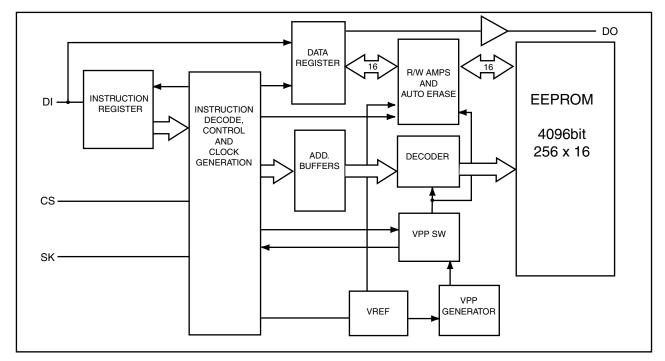

### 2.Block diagram

### 3.Pin function

| Pin No. | Symbol | Function                                        |

|---------|--------|-------------------------------------------------|

| 1       | PE     | Program enable (With built-in pull up resistor) |

| 2       | VCC    | Power supply                                    |

| 3       | CS     | Chip selection                                  |

| 4       | SK     | Serial clock input                              |

| 5       | DI     | Serial data input                               |

| 6       | DO     | Serial data output                              |

| 7       | GND    | Ground                                          |

| 8       | NC     | No connection                                   |

Note : The pull-up resistor of the PE pin is about 2.5 M  $\Omega$  (VCC=5V)

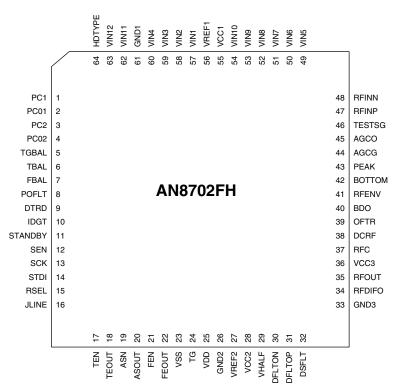

## AN8702FH (IC101) : Frontend processor

#### 2. Pin function

| Pin No. | Symbol  | I/O | Function                                                          | Pin No. | Symbol | I/O | Function                                                 |

|---------|---------|-----|-------------------------------------------------------------------|---------|--------|-----|----------------------------------------------------------|

| 1       | PC1     |     |                                                                   | 33      | GND3   | -   | Earth terminal 3                                         |

| 2       | PC01    |     |                                                                   | 34      | RFDIFO |     |                                                          |

| 3       | PC2     |     |                                                                   | 35      | RFOUT  |     |                                                          |

| 4       | PC02    |     |                                                                   | 36      | VCC3   | -   | Power terminal 3 (5V)                                    |

| 5       | TGBAL   | Ι   | Tangential phase balance control terminal                         | 37      | RFC    |     |                                                          |

| 6       | TBAL    | Ι   | Tracking balance control terminal                                 | 38      | DCRF   | 0   | BDO output terminal                                      |

| 7       | FBAL    | Ι   | Focus balance control terminal                                    | 39      | OFTR   | 0   | OFTR output terminal                                     |

| 8       | POFLT   | 0   | Track detection threshold value level terminal                    | 40      | BDO    | 0   | BDO output terminal                                      |

| 9       | DTRD    | Ι   | Data slice data read signal input terminal (For RAM)              | 41      | RFENV  | 0   | RF enve output terminal                                  |

| 10      | IDGT    | Ι   | Data slice part address part gate signal input terminal (For RAM) | 42      | воттом | 0   | Bottom enve detection filter terminal                    |

| 11      | STANDBY | Ι   | Standby mode control terminal                                     | 43      | PEAK   | 0   | Peak enve detection filter terminal                      |

| 12      | SEN     | Ι   | SEN(Sereal data input terminal)                                   | 44      | AGCG   | 0   | AGC amplifier gain control terminal                      |

| 13      | SCK     | Ι   | SCK(Sereal data input terminal)                                   | 45      | AGCO   |     |                                                          |

| 14      | STDI    | Ι   | STDI(Sereal data input terminal)                                  | 46      | TESTSG | Т   | TEST signal input terminal                               |

| 15      | RSEL    |     |                                                                   | 47      | RFINP  | Т   | RF signal positive moving input terminal                 |

| 16      | JLINE   |     |                                                                   | 48      | RFINN  | Т   | RF signal reversing input terminal                       |

| 17      | TEN     |     |                                                                   | 49      | VIN5   | Т   | Focus input of external division into two terminal       |

| 18      | TEOUT   | 0   | Tracking error signal output terminal                             | 50      | VIN6   | Ι   | Focus input of external division into two terminal       |

| 19      | ASN     |     |                                                                   | 51      | VIN7   | Ι   |                                                          |

| 20      | ASOUT   |     |                                                                   | 52      | VIN8   | Ι   |                                                          |

| 21      | FEN     | Ι   | Focus error output amplifier reversing input terminal             | 53      | VIN9   | Τ   |                                                          |

| 22      | FEOUT   | 0   | Focus error signal output terminal                                | 54      | VIN10  | Ι   |                                                          |

| 23      | VSS     | -   | Earth terminal                                                    | 55      | VCC1   | -   | Power terminal 1                                         |

| 24      | TG      | 0   | Tangential phase error signal output terminal                     | 56      | VREF1  | 0   | VREF1 voltage output terminal                            |

| 25      | VDD     | -   | Power terminal (3V)                                               | 57      | VIN1   | Ι   | External division into four (DVD/CD) RF input terminal 1 |

| 26      | GND2    | -   | Earth terminal 2                                                  | 58      | VIN2   | Ι   | External division into four (DVD/CD) RF input terminal 2 |

| 27      | VREF2   | 0   | VREF2 voltage output terminal                                     | 59      | VIN3   | Ι   | External division into four (DVD/CD) RF input terminal 3 |

| 28      | VCC2    | -   | Power terminal (5V)                                               | 60      | VIN4   | Ι   | External division into four (DVD/CD) RF input terminal 4 |

| 29      | VHALF   | 0   | VHALF voltage output terminal                                     | 61      | GND1   | -   | Earth terminal 1                                         |

| 30      | DFLTON  |     |                                                                   | 62      | VIN11  | Ι   |                                                          |

| 31      | DFLTOP  |     |                                                                   | 63      | VIN12  | Ι   |                                                          |

| 32      | DSFLT   |     |                                                                   | 64      | HDTYPE |     |                                                          |

AN8702FH

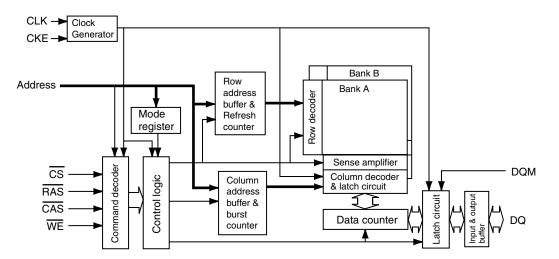

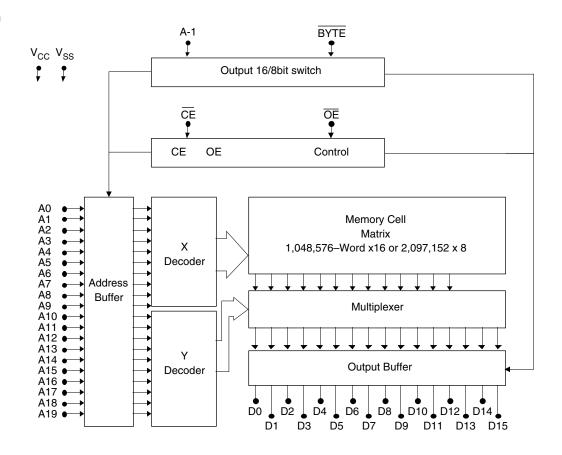

## ■ HY57V161610DTC8 or W981616AH-7 or K4S161622D-TC80 (IC504,IC505) : 16MB SDRAM

1.Block diagram

#### 2.Pin function

| Pin No. | Symbol | Description           | Pin No. | Symbol  | Description          |

|---------|--------|-----------------------|---------|---------|----------------------|

| 1       | VCC    | Power supply          | 26      | VSS     | Connect to GND       |

| 2,3     | DQ0,1  | Data input/output     | 27~32   | A4~9    | Address inputs       |

| 4       | VSS    | Connect to GND        | 33      | NC      | Non connect          |

| 5,6     | DQ2,3  | Data input/output     | 34      | CKE     | Clock enable         |

| 7       | VDD    | Power supply          | 35      | CLK     | System clock input   |

| 8,9     | DQ4,5  | Data input/output     | 36      | UDQM    | Upper DQ mask enable |

| 10      | VSS    | Connect to GND        | 37      | NC      | Non connect          |

| 11,12   | DQ6,7  | Data input/output     | 38      | VCC     | Power supply         |

| 13      | VCC    | Power supply          | 39,40   | DQ8,9   | Data input/output    |

| 14      | LDQM   | Lower DQ mask enable  | 41      | VSS     | Connect to GND       |

| 15      | WE     | Write enable          | 42,43   | DQ10,11 | Data input/output    |

| 16      | CAS    | Column address strobe | 44      | VDD     | Power supply         |

| 17      | RAS    | Row address strobe    | 45,46   | DQ12,13 | Data input/output    |

| 18      | CS     | Chip enable           | 47      | VSS     | Connect to GND       |

| 19,20   | A11,10 | Address inputs        | 48,49   | DQ14,15 | Data input/output    |

| 21~24   | A0~3   | Address inputs        | 50      | VSS     | Connect to GND       |

| 25      | VCC    | Power supply          |         |         |                      |

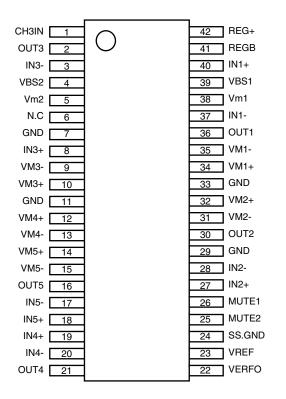

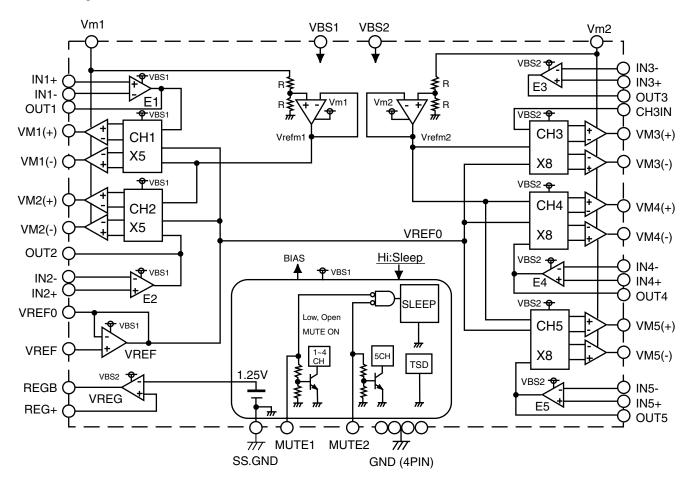

### ■ M56788FP-W(IC271) : Traverse mechanism driver

#### 1.Pin layout

2.Block diagram

## **Discription of major IC's**

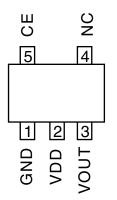

## ■ AK93C65AF-X(IC403) : EEPROM

1.Terminal layout

### 2.Block diagram

### 3.Pin function

| Pin No. | Symbol | Function                                        |

|---------|--------|-------------------------------------------------|

| 1       | PE     | Program enable (With built-in pull up resistor) |

| 2       | VCC    | Power supply                                    |

| 3       | CS     | Chip selection                                  |

| 4       | SK     | Serial clock input                              |

| 5       | DI     | Serial data input                               |

| 6       | DO     | Serial data output                              |

| 7       | GND    | Ground                                          |

| 8       | NC     | No connection                                   |

Note : The pull-up resistor of the PE pin is about 2.5 M  $\Omega$  (VCC=5V)

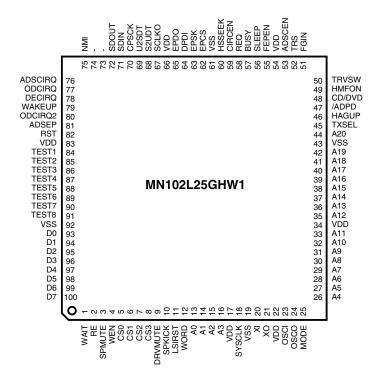

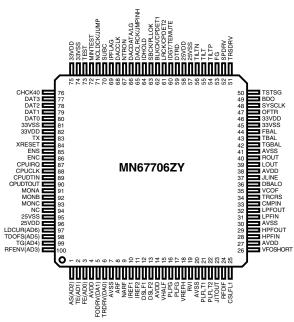

## MN102L25GHW1(IC401) : UNIT CPU

#### 1. Pin layout

#### 2.Pin function

| Pin No.         | Symbol     | I/O | Function                                         | Pin No.  | Symbol         | I/O      | Function                                   |

|-----------------|------------|-----|--------------------------------------------------|----------|----------------|----------|--------------------------------------------|

| 1               | WAIT       | 1   | Micon wait signal input                          | 51       | FGIN           | 1        | Photo input                                |

| 2               | RE         | 0   | Read enable                                      | 52       | TRS            |          | ·                                          |

| 3               | SPMUTE     | 0   |                                                  | 53       | ADSCEN         | 0        | Serial enable signal for ADSC              |

| 4               | WEN        | 0   | Write enable                                     | 54       | VDD            | -        | Power supply                               |

| 5               | CS0        | 0   | Non connect                                      | 55       | FEPEN          | 0        | Serial enable signal for FEP               |

| 6               | CS1        | 0   | Chip select for ODC                              | 56       | SLEEP          | 0        | Standby signal for FEP                     |

| 7               | CS2        | 0   | Chip select for ZIVA                             | 57       | BUSY           |          | Communication busy                         |

| 8               | CS3        | 0   | Chip select for outer ROM                        | 58       | REQ            | 0        | Communication request                      |

| 9               | DRVMUTE    | 0   | Driver mute                                      | 59       | CIRCEN         | 0        | CIRC command select                        |

| 10              | SPKICK     | 0   | Non connect (Spin kick output)                   | 60       | HSSEEK         | 0        | Seek select                                |

| 11              | LSIRST     | 0   | LSI reset                                        | 61       | VSS            | -        | GND                                        |

| 12              | WORD       | 0   | Bus selection input                              | 62       | EPCS           | 0        | Chip select signal for EEPROM              |

| 13              | A0         | Ō   | Address bus 0 for CPU                            | 63       | EPSK           | Ō        | Clock signal for EEPROM                    |

| 14              | A1         | 0   | Address bus 1 for CPU                            | 64       | DPDI           | 1 I      | Input data for EEPROM                      |

| 15              | A2         | Ō   | Address bus 2 for CPU                            | 65       | EPDO           | Ó        | Output data for EEPROM                     |

| 16              | A3         | Ō   | Address bus 3 for CPU                            | 66       | VDD            | -        | Power supply                               |

| 17              | VDD        | -   | Power supply                                     | 67       | SCLKO          | 1        | Communication clock                        |

| 18              | SYSCLK     | 0   | System clock signal output                       | 68       | S2UDT          | 1 i      | Communication input data                   |

| 19              | VSS        | -   | GND                                              | 69       | U2SDT          | Ó        | Communication output data                  |

| 20              | XI         | -   | Non connect (Connect to VSS)                     | 70       | CPSCK          | 0        | Clock for ADSC serial                      |

| 21              | XO         | -   | Non connect                                      | 71       | SDIN           | Ĭ        | ADSC serial data input                     |

| 22              | VDD        | -   | Power supply                                     | 72       | SDOUT          | Ó        | ADSC serial data output                    |

| 23              | OSCI       | 1   | Clock signal input (13.5MHz)                     | 72       | -              | -        | Non connect                                |

| 24              | OSCO       | 0   | Clock signal output (13.5MHz)                    | 74       | -              | -        | Non connect                                |

| 25              | MODE       | Ĭ   | CPU Mode selection input                         | 75       | NMI            | -        | Non connect                                |

| 26              | A4         | 0   | Address bus 4 for CPU                            | 75       | ADSCIRQ        |          | Interrupt input of ADSC                    |

| 27              | A5         | 0   | Address bus 5 for CPU                            | 70       | ODCIRQ         |          | Interrupt input of ODC                     |

| 28              | A6         | 0   | Address bus 6 for CPU                            | 78       | DECIRQ         | +        | Interrupt input of ZIVA                    |

| 29              | A0<br>A7   | 0   | Address bus 7 for CPU                            | 70       | WAKEUP         | 0        | Non connect                                |

| 30              | A7<br>A8   | 0   | Address bus 7 for CPU                            | 80       | ODCIRQ2        |          | Non connect                                |

| 31              | A9         |     | Address bus 9 for CPU                            | 81       | ADSEP          | +        | Address data selection input               |

| 32              | A9<br>A10  | 0   | Address bus 10 for CPU                           | 82       | RST            |          | Reset input                                |

| 33              | A10        | 0   | Address bus 10 for CPU                           | 83       | VDD            |          | Power supply                               |

| 34              | VDD        | -   | Power supply                                     | 84       | TEST1          |          | Test signal 1 input                        |

| 35              | A12        | 0   | Address bus 12 for CPU                           | 85       | TEST2          |          | Test signal 2 input                        |

| 36              | A12<br>A13 | 0   | Address bus 12 for CPU<br>Address bus 13 for CPU | 86       | TEST3          |          | Test signal 3 input                        |

| 30              | A13        | 0   | Address bus 13 for CPU                           | 87       | TEST4          |          | Test signal 4 input                        |

| 38              | A14<br>A15 | 0   | Address bus 14 for CPU<br>Address bus 15 for CPU | 88       | TEST5          |          | Test signal 5 input                        |

|                 | -          | 0   |                                                  |          |                |          |                                            |

| <u>39</u><br>40 | A16<br>A17 | 0   | Address bus 16 for CPU<br>Address bus 17 for CPU | 89<br>90 | TEST6<br>TEST7 |          | Test signal 6 input<br>Test signal 7 input |

| 40              | A17<br>A18 | 0   | Address bus 17 for CPU<br>Address bus 18 for CPU | 90       | TEST8          |          | Test signal 8 input                        |

|                 | -          | 0   |                                                  | -        | VSS            |          | GND                                        |

| 42<br>43        | A19<br>VSS | -   | Address bus 19 for CPU<br>GND                    | 92       | D0             | -<br>I/O | Data bus 0 of CPU                          |

| -               |            | -   | Address bus 20 for CPU                           |          | -              |          |                                            |

| 44              | A20        | 0   |                                                  | 94       | D1             | 1/0      | Data bus 1 of CPU                          |

| 45              | TXSEL      | 0   | TX select                                        | 95       | D2             | 1/0      | Data bus 2 of CPU                          |

| 46              | HAGUP      | 0   |                                                  | 96       | D3             | 1/0      | Data bus 3 of CPU                          |

| 47              | /ADPD      | -   |                                                  | 97       | D4             | 1/0      | Data bus 4 of CPU                          |

| 48              | CD/DVD     | 0   |                                                  | 98       | D5             | 1/0      | Data bus 5 of CPU                          |

| 49              | HMFON      | +   |                                                  | 99       | D6             | 1/0      | Data bus 6 of CPU                          |

| 50              | TRVSW      |     | Detection switch of traverse inside              | 100      | D7             | I/O      | Data bus 7 of CPU                          |

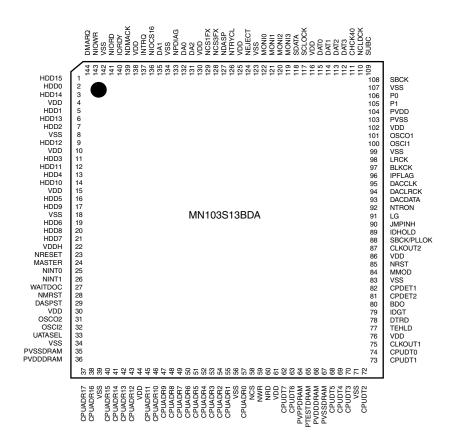

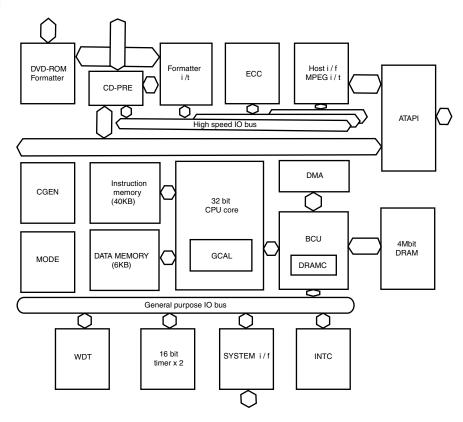

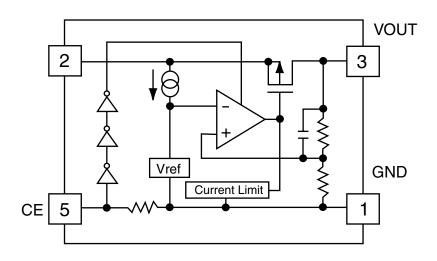

## MN103S13BDA(IC301) : Optical disc controller

1. Pin layout

2.Block diagram

### 3.Pin function

| Dist                                   | Cumhal                                                            | 1/0                  | Function                                                                                                      | Dia Ma                          | Quarte el                       | 1/0             | Evention                                                                                                                            |

|----------------------------------------|-------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                | Symbol                                                            | 1/0                  | Function                                                                                                      | Pin No.                         | Symbol                          | I/O             | Function                                                                                                                            |

| 1                                      | HDD15<br>HDD0                                                     | I/O<br>I/O           | ATAPI data                                                                                                    | 73<br>74                        | CPUDT1<br>CPUDT0                | I/O             | System control data                                                                                                                 |

| 3                                      | HDD0<br>HDD14                                                     | 1/O                  | ATAPI data<br>ATAPI data                                                                                      | 74                              | CPUDIU<br>CLKOUT1               | 1/O<br>0        | System control data<br>16.9/11.2/8.45MHz clock                                                                                      |

| 4                                      | VDD                                                               | -                    | Power supply (3V)                                                                                             | 76                              | VDD                             | -               | Power supply (3V)                                                                                                                   |

| 5                                      | HDD1                                                              | I/O                  | ATAPI data                                                                                                    | 77                              | TEHLD                           | 0               | Mirror gate (Connect with TP141)                                                                                                    |

| 6                                      | HDD13                                                             | 1/O                  | ATAPI data                                                                                                    | 78                              | DTRD                            | Ō               | Frequency control switch for data (Connect with TP304)                                                                              |

| 7                                      | HDD2                                                              | I/O                  | ATAPI data                                                                                                    | 79                              | IDGT                            | 0               | Part CAPA switch                                                                                                                    |

| 8                                      | VSS                                                               | -                    | GND                                                                                                           | 80                              | BDO                             | I               | RF dropout / BCA data                                                                                                               |

| 9                                      | HDD12                                                             | I/O                  | ATAPI data                                                                                                    | 81                              | CPDET2                          | I               | Outer side CAPA detection                                                                                                           |

| 10                                     | VDD                                                               | -                    | Power supply (2.7V)                                                                                           | 82                              | CPDET1                          |                 | Inner side CAPA detection                                                                                                           |

| 11                                     | HDD3                                                              | I/O                  | ATAPI data                                                                                                    | 83                              | VSS                             | -               | GND                                                                                                                                 |

| 12<br>13                               | HDD11<br>HDD4                                                     | I/O<br>I/O           | ATAPI data<br>ATAPI data                                                                                      | 84<br>85                        | MMOD<br>NRST                    |                 | Connect with VSS<br>System reset                                                                                                    |

| 13                                     | HDD4<br>HDD10                                                     | 1/0                  | ATAPI data                                                                                                    | 86                              | VDD                             | -               | Power supply (3V)                                                                                                                   |

| 15                                     | VDD                                                               | -                    | Power supply (3V)                                                                                             | 87                              | CLKOUT2                         | 0               | 16.9MHz clock                                                                                                                       |

| 16                                     | HDD5                                                              | I/O                  | ATAPI data                                                                                                    | 88                              | SBCK/PLLOK                      | 0               | Frame mark detection                                                                                                                |

| 17                                     | HDD9                                                              | I/O                  | ATAPI data                                                                                                    | 89                              | IDOHOLD                         | 0               | ID gate for holding tracking                                                                                                        |

| 18                                     | VSS                                                               | -                    | GND                                                                                                           | 90                              | JMPINH                          | 0               | Jump prohibition                                                                                                                    |

| 19                                     | HDD6                                                              | I/O                  | ATAPI data                                                                                                    | 91                              | LG                              | 0               | Land / group switch                                                                                                                 |

| 20                                     | HDD8                                                              | I/O                  | ATAPI data                                                                                                    | 92                              | NTRON                           | 1               | Tracking ON                                                                                                                         |

| 21                                     | HDD7                                                              | I/O                  | ATAPI data                                                                                                    | 93                              | DACDATA                         | 0               | Serial output                                                                                                                       |

| 22                                     | VDDH                                                              | <u> </u>             |                                                                                                               | 94                              | DACLRCK                         | 0               | L and R identification output                                                                                                       |

| 23<br>24                               | NRESET<br>MASTER                                                  | I/O                  | ATAPI reset<br>ATAPI master / slave selection                                                                 | 95<br>96                        | DACCLK<br>IPFLAG                |                 | Clock for serial output                                                                                                             |

| 24                                     | NINT0                                                             | 0                    |                                                                                                               | 96<br>97                        | BLKCK                           |                 | IP flag input                                                                                                                       |

| 25                                     | NINT1                                                             | 0                    | System control interruption 0<br>System control interruption 1                                                | 97<br>98                        | LRCK                            |                 | Clock for sub-code and block input<br>L and R identification signal output                                                          |

| 20                                     | WAITDOC                                                           | 0                    | System control wait control                                                                                   | 98                              | VSS                             | -               | GND                                                                                                                                 |

| 28                                     | NMRST                                                             | 0                    | System control reset (Connect with TP302)                                                                     | 100                             | OSCI1                           | -               | 16.9MHz oscillation                                                                                                                 |

| 29                                     | DASPST                                                            | Ĭ                    | DASP signal initializing                                                                                      | 100                             | OSCO1                           | 0               | 16.9MHz oscillation                                                                                                                 |

| 30                                     | VDD                                                               | -                    | Power supply (3V)                                                                                             | 102                             | VDD                             | -               | Power supply (3V)                                                                                                                   |

| 31                                     | OSCO2                                                             | 0                    | Not used (Connect with TP140)                                                                                 | 102                             | PVSS                            | -               | GND                                                                                                                                 |

| 32                                     | OSCI2                                                             | Ī                    | Not used (Connect with TP303)                                                                                 | 104                             | PVDD                            | -               | Power supply (3V)                                                                                                                   |

| 33                                     | UATASEL                                                           | l i                  | VSS connection                                                                                                | 105                             | P1                              | I/O             | Terminal MASTER polarity switch input                                                                                               |

| 34                                     | VSS                                                               | -                    | GND                                                                                                           | 106                             | P0                              | I/O             | CIRC-RAM OVER/UNDER Interruption signal input                                                                                       |

| 35                                     | PVSSDRAM                                                          |                      | VSS connection                                                                                                | 107                             | VSS                             | -               | GND                                                                                                                                 |

| 36                                     | PVDDDRAM                                                          |                      | Connect with 2.7V VDD                                                                                         | 108                             | SBCK                            | 0               | Sub-code and Clock output for serial input                                                                                          |

| 37                                     | CPUADR17                                                          |                      | System control address                                                                                        | 109                             | SUBC                            | I               | Sub-code and serial input                                                                                                           |

| 38                                     | CPUADR18                                                          | 1                    | System control address                                                                                        | 110                             | NCLDCK                          | 1               | Sub-code and Frame clock input                                                                                                      |

| 39                                     | VSS                                                               | -                    | GND                                                                                                           | 111                             | CHCK40                          | I               | Read clock to DAT3~0 (Output of dividing frequency four from ADSC)                                                                  |

| 40                                     | CPUADR15                                                          |                      | System control address                                                                                        | 112                             | DAT3                            | 1               | Read data from DISC (Parallel output from ADSC)                                                                                     |

| 41                                     | CPUADR14                                                          |                      | System control address                                                                                        | 113                             | DAT2                            |                 | Read data from DISC (Parallel output from ADSC)                                                                                     |

| 42                                     | CPUADR13                                                          |                      | System control address                                                                                        | 114                             | DAT1                            |                 | Read data from DISC (Parallel output from ADSC)                                                                                     |

| 43                                     | CPUADR12                                                          |                      | System control address                                                                                        | 115                             | DAT0                            | -               | Read data from DISC (Parallel output from ADSC)                                                                                     |

| 44<br>45                               | VDD<br>CPUADR11                                                   | -                    | Power supply (2.7V)                                                                                           | 116<br>117                      | VDD<br>SCLOCK                   | -<br>I/O        | Power supply (3V)                                                                                                                   |

| 45                                     | CPUADR11<br>CPUADR10                                              |                      | System control address<br>System control address                                                              | 117                             | SDATA                           | 1/O<br>1/O      | Debugging serial clock (270 $\Omega$ pull up)<br>Debugging serial data (270 $\Omega$ pull up)                                       |

| 46                                     | CPUADR10<br>CPUADR9                                               |                      | System control address<br>System control address                                                              | 118                             | MONI3                           | 0               | Internal goods title monitor (Connect to TP150)                                                                                     |

| 47                                     | CPUADR9<br>CPUADR8                                                |                      | System control address                                                                                        | 120                             | MONI2                           | 0               | Internal goods title monitor (Connect to TP150)                                                                                     |

| 40                                     | CPUADR7                                                           |                      | System control address                                                                                        | 120                             | MONI1                           | 0               | Internal goods title monitor (Connect to TP157)                                                                                     |

| 50                                     | CPUADR6                                                           | i                    | System control address                                                                                        | 122                             | MONIO                           | 0               | Internal goods title monitor (Connect to TP153)                                                                                     |

| 51                                     | CPUADR5                                                           | i                    | System control address                                                                                        | 123                             | VSS                             | -               | GND                                                                                                                                 |

| 52                                     | CPUADR4                                                           | i                    | System control address                                                                                        | 124                             | NEJECT                          | 1               | Eject detection                                                                                                                     |

| 53                                     | CPUADR3                                                           | i                    | System control address                                                                                        | 125                             | VDD                             | -               | Power supply (2.7V)                                                                                                                 |

| 54                                     | CPUADR2                                                           | 1                    | System control address                                                                                        | 126                             | NTRYCL                          | Ι               | Tray close detection                                                                                                                |

| 55                                     | CPUADR1                                                           | I                    | System control address                                                                                        | 127                             | NDASP                           | I/O             | ATAPI Drive active/Slave connection I/O                                                                                             |

| 56                                     | VSS                                                               | -                    | GND                                                                                                           | 128                             | NCS3FX                          | I               | Not used (ATAPI host chip selection)                                                                                                |

| 57                                     | CPUADR0                                                           |                      | System control address                                                                                        | 129                             | NCS1FX                          |                 | Not used (ATAPI host chip selection)                                                                                                |

| 58                                     | NCS                                                               |                      | System control chip selection                                                                                 | 130                             | VDD                             | -               | Power supply (3V)                                                                                                                   |

| 59                                     | NWR                                                               |                      | System control write                                                                                          | 131                             | DA2                             | I/O             | ATAPI host address                                                                                                                  |

| 60                                     | NRD                                                               | 1                    | System control read                                                                                           | 132                             | DA0                             | I/O             | Not used (ATAPI host address)                                                                                                       |

| 61                                     | VDD                                                               | -                    | Power supply (3V)                                                                                             | 133                             | NPDIAG                          | I/O             | ATAPI slave/master diagnosis input                                                                                                  |

|                                        | CPUDT7                                                            | I/O<br>I/O           | System control data                                                                                           | 134                             | VSS                             | -<br>I/O        | GND                                                                                                                                 |

| 62                                     |                                                                   | i I/O                | System control data                                                                                           | 135<br>136                      | DA1<br>NIOCS16                  | 0               | Not used (ATAPI host address)<br>ATAPI output for selecting width of host data bus                                                  |

| 63                                     | CPUDT6                                                            |                      |                                                                                                               |                                 | 11100310                        |                 | ATAPT OUTPUT OF SELECTING WIDTH OF HOST DATA DUS                                                                                    |

| 63<br>64                               | PVPPDRAM                                                          | 0                    | Connect with VSS                                                                                              |                                 |                                 | 0               | ATAPI host interruption output                                                                                                      |

| 63<br>64<br>65                         | PVPPDRAM<br>PTESTDRAM                                             |                      | Connect with VSS                                                                                              | 137                             |                                 | 0               | ATAPI host interruption output                                                                                                      |